# HALCoGen EMAC Driver with IwIP Demonstration

## v00.04.00

# **User Guide**

## 14th August 2019

Copyright  $\ensuremath{\textcircled{C}}$  2003-2019 Texas Instruments Incorporated. All rights reserved.

Information in this document is subject to change without notice. Texas Instruments may have pending patent applications, trademarks, copyrights, or other intellectual property rights covering matter in this document. The furnishing of this documents is given for usage with Texas Instruments products only and does not give you any license to the intellectual property that might be contained within this document. Texas Instruments makes no implied or expressed warranties in this document and is not responsible for the products based from this document.

HALCoGen EMAC Driver with IwIP Demonstration v00.04.00

#### 1 Introduction

The Ethernet Media Access Controller (EMAC) and Management Data Input/Output (MDIO) peripherals on the Hercules line of devices provide a full-featured Ethernet interface. The EMAC peripheral conforms to the IEEE 802.3 standard, describing the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer specifications. The EMAC module provides an efficient interface between the processor and a local network. The EMAC supports 10Base-T (10 Mbps) and 100BaseTX (100 Mbps), in half-duplex and full-duplex modes. The EMAC control module provides an interface from the CPU to the EMAC and MDIO modules. The EMAC control module controls device interrupts and incorporates an 8k-byte internal RAM to hold EMAC buffer descriptors (also known as CPPI RAM). The MDIO module implements the 802.3 serial management interface to interrogate and control up to 32 Ethernet PHYs connected to the device by using a shared two-wire bus. Applications can use the MDIO module to configure the auto negotiation parameters of each PHY attached to the EMAC, retrieve the negotiation results, and configure required parameters in the EMAC module for correct operation.

The driver code is part of the HALCoGen release and APIs for EMAC and MDIO are listed in *include/emac.h* and *include/mdio.h*, respectively.

#### **2** Supported Features

.

Integration of CPDMA based EMAC driver for RM48xx/RM46xx/TMS570xxx/RM57xx/TMS570LCxx

- IwIP 1.4.1 TCP/IP stack ported for the above devices' EMAC driver

- By default DHCP support is enabled. However the integration supports both DHCP & Static IP addressing.

- Integration with HALCoGen v04.07.01 release

- By default the software is configured for executing from flash.

- The integrated application demonstrates a webserver application on a TMS570xx/TMS570LCxx/RM48xx/RM57xx Hardware development kit (HDK).

- Diagnostic & Debug messages are printed on JTAG SCI Port. Following are the settings for the console:

- Baud Rate: 9600 Data: 8 bit Parity: None Stop bit: 1 Flow Control: None

<u>Note</u>: Since the MAC Address is part of the binary image, all devices programmed with these binaries & connected to same DHCP server will be assigned same IP address. The default MAC address is 00:08:EE:03:A6:6C

#### What's new:

- Integration with HALCoGen v04.07.01 release

- Added LAUNCHXL2 570LC43x and LAUNCHXL2 RM57x support

# TEXAS INSTRUMENTS

### 3 Configuring EMAC and MDIO using HALCoGen GUI

The following sequence is to be followed to get working driver code for EMAC and MDIO modules using HALCoGen. A working implementation of this with IwIP is available at the end of this page. (For TMS570LC43xx and RM57x devices, follow the instructions after this set.)

- 1. Under the 'Driver Enable' tab, enable EMAC Driver and SCI2 Driver.

- 2. Under 'VIM RAM' add the names of the ISRs for EMAC Transmit and Receive Interrupts (Channels 77 and 79 respectively).

- 3. Enable these interrupts under the 'VIM Channel 64-95' tab.

- 4. Under the 'PLL' tab, change the multiplier for both PLLs to a value of 120, such that the output frequency in both cases is 160.00 MHz.

- 5. Under the 'GCM' tab, change the value of the VCLKA4 Divider to 2, such that the output of VCLKA4( or VCLKA4\_DIVR\_EMAC in case of RM46x/TMS570LS12x Devices) is 40.00 MHz.

- 6. Under the 'PINMUX' tab, enable RMII/MII, MDIO(G3) & MDCLK(V5).

- 7. Under the 'EMAC' tab, change the EMAC address to the correct address (the default one is mentioned above). Change the physical address to 1.

- 8. Generate the system initialization and HAL Code.

#### For TMS570LC43x and RM57x devices:

- 1. Under the 'Driver Enable' tab, enable EMAC Driver and SCI1 Driver.

- 2. Under 'VIM RAM' add the names of the ISRs for EMAC Transmit and Receive Interrupts (Channels 77 and 79 respectively).

- 3. Enable these interrupts under the 'VIM Channel 64-95' tab.

- 4. Under the 'PLL' tab, change the multiplier for both PLLs to a value of 150, such that the output frequency in both cases is 300.00 MHz.

- 5. Under the 'GCM' tab, change the value of the VCLK1, VCLK2 and VCLK3 Dividers to 1 and VCLKA4 Divider to 2, such that the output of VCLKA4\_DIV is 37.50 MHz.

- Under the 'PINMUX' tab, enable RMII/MII, under Pin Muxing. Under Input Muxing, enable MDIO(G3), MII\_COL(F3), MII\_CRS(B4), MII\_RX\_DV(B11), MII\_RX\_ER(N19), MII\_RXCLK(K19), MII\_RXD[0], MII\_RXD[1], MII\_RXD[2], MII\_RXD[3], MII\_TX\_CLK.

- 7. Under the 'EMAC' tab, change the EMAC address to the correct address (the default one in the example is mentioned above). The physical address is 1 by default.

- 8. Generate the system initialization and HAL Code.

### 4 **Programming Sequence using HALCoGen generated drivers**

Using the HALCoGen generated driver code (through the procedure above), the following sequence can be used to configure and operate the EMAC and MDIO modules.

1. Initialize the EMAC module by calling *EMACInit()*. This API resets the EMAC and EMAC Control Module Registers.

- 2. Initialize the MDIO Module using **MDIOInit()**. Insert a short delay after this function returns to ensure that MDIO module initialization completes successfully before using other MDIO APIs.

- 3. Auto negotiate with the PHY device connected to MDIO. PHY Auto negotiation APIs are provided as reference and must be adapted to the external PHY present on the hardware.

- 4. After completing auto negotiation, get the auto negotiation result using the respective PHY's link partner ability API and set the duplex mode of operation in the EMAC using **EMACDuplexSet()**.

- 5. Set the MAC Address in the EMAC hardware using EMACMACAddrSet()

- 6. Enable unicast for a specific channel using the *EMACRxUnicastSet()* API (optional).

- 7. Initialize the TX and RX buffer descriptors in the CPPI RAM, which is local to the EMAC.

- 8. Enable the TX operation in EMAC using **EMACTxEnable()**. This enables the EMAC hardware transmit operation. However, transmission will not start until a valid descriptor pointer is written using EMACTxHdrDescPtrWrite().

- 9. Enable the RX operation in EMAC using *EMACRXEnable()*.

- 10. Write the RX Header Descriptor Pointer using *EMACRxHdrDescPtrWrite()*. The EMAC hardware will start receiving data at this point. The data will be stored to the buffer pointer in this buffer descriptor. After the buffer corresponding to this descriptor is filled, the next descriptor is used by the EMAC hardware according to the buffer descriptor settings.

- 11. Enable MII using *EMACMIIEnable()*.

- 12. Enable the Transmit and Receive Pulse interrupts

using **EMACTxIntPulseEnable()** and **EMACRxIntPulseEnable()**. The interrupts will be routed through the EMAC Control Core to the CPU interrupt controller. This enables the EMAC TX and RX pulse interrupts at EMAC peripheral level only. The core interrupts must be enabled separately in the VIM.

The following guidelines should be observed when writing an EMAC interrupt service routine (ISR):

- In an EMAC Transmit ISR, the interrupt must be acknowledged to the EMAC hardware using *EMACCoreIntAck()*. However, the interrupt will be cleared only if the completion pointer is written using the EMACTxCPWrite() API with the last processed TX buffer descriptor.

- In an EMAC Receive ISR, the interrupt must be acknowledged to the EMAC hardware using *EMACCoreIntAck()*. Again, the interrupt will be cleared only if the completion pointer is written using the EMACRxCPWrite() API with the last processed RX buffer descriptor.

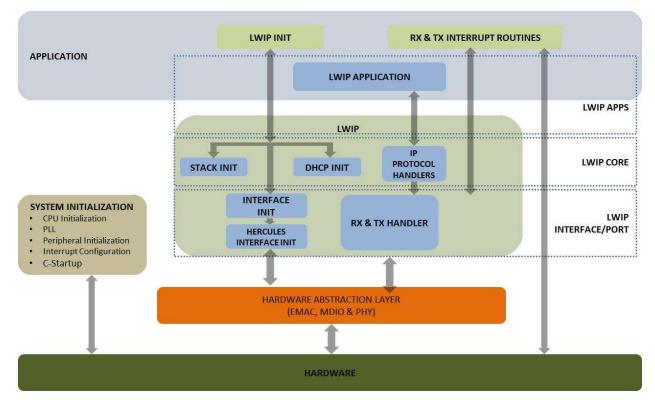

### 5 Design of LwIP Integration

The integrated software deliverable consists of four main layers:

- 1. Hardware Abstraction Layer (HAL): EMAC & MDIO HALs are part of the HALCoGen release and the PHY HAL is part of the application.

- 2. IwIP Network Interface Layer Hercules NetIF port for LwIP

- 3. IWIP Application Layer An IP stack application based on LwIP. Examples are provided for HTTP server, UDP based client and echo server. The packets start and end at this layer.

- 4. System Application Layer This includes the system initialization and is generated based on the HALCoGen GUI. This layer configures the PLLs & PINMUX.

#### 5.1 Hardware Abstraction Layer

This layer implements the lowers level hardware abstraction APIs that can be used for control and configuration of the EMAC device.

- *emac.c* Ethernet MAC and Control module. This file is generated using HALCoGen. In this release the file is located at *<Device>\HALCoGen-xx\source\emac.c*, where xx is the device variant.

- *mdio.c* MDIO interface between the PHY and MAC. This file is generated using HALCoGen. In this release the file is located at <*Device*>\*HALCoGen-xx*\*source*\*emac.c*

- *phy\_dp83640.c* Example PHY Device HAL for DP83640 PHY on HDK. This file should be written for the external Ethernet PHY on the hardware.

### 5.2 IwIP Interface Layer

To interface with the rest of the network, the device abstraction layer needs to be glued with a network stack that can form and interpret network packets. The device abstraction hooks into the interface layer of lwIP. This is also referred to as the device-specific "port" or the hdk-interface for lwIP. It defines standard interface entry points and state variables. A network device is represented by struct netif, generically referred to as netif. The netif contains all the information about the interface, including the IP/MAC address(s), TCP/IP options, protocol handlers, link information, and (most importantly) the network device driver entry point callbacks. Every network interface must implement the linkoutput and init callbacks, and all state information is maintained in this structure. The interface layer also implements the core interrupt handling and DMA handling. All the required function calls for initializing the lwIP stack and registering the network interface are performed in *lwip*-

*1.3.2\ports\hdk\lwiplib.c\lwiplib.c*. Refer to the lwIP documentation for more information about the lwIP stack implementation.

#### 6 Hercules Development Network Interface Layer

The main tasks of the HDK Interface layer are:

#### 6.1 Network device initialization

The first step towards bringing up the interface is done as part of the hdkif\_init(). This function is called when the network device is registered with the lwIP stack using netif\_add. As part of the initialization, the netif output callbacks are registered and hardware initialization, including PHY and DMA initialization, is performed. DMA buffer descriptor (BD) pools are maintained in the CPPI RAM for both TX and RX channels. The descriptor chains are maintained by the "free\_head", which points to the next unused/free descriptor in the BD pool, and "active\_tail", which points to the last BD in the active queue that has been en-queued to the hardware. The packet buffers (pbuf) are pre-allocated for maximum length and queued in the receive buffer descriptors before the reception begins. Please refer to the lwIP documentation for details on pbuf handling by lwIP.

#### 6.2 Packet Data Transmission

Packet data transmission takes place inside the linkoutput callback registered with the lwIP stack. This callback is invoked whenever the lwIP stack receives a packet for transmission from the application layer. The pbuf can contain a chain of packet buffers and hence the DMA descriptors are properly updated (chained if necessary), with SOP, EOP and length fields. The first DMA descriptor is marked with the EOP and OWNER flags, while only the last is set with the EOP flag. After filling the BD's with the pbuf information, the BD, which corresponds to the SOP is written to the HEAD descriptor pointer register to start the transmission. Once a packet is transmitted, the EMAC Control Core generates a transmit interrupt. This interrupt is cleared only if the completion pointer is written with the last BD processed. In the interrupt handler, the next BD to process is taken and traversed to reach the BD that corresponds to the end of the packet. This BD, which corresponds to the end of the packet.

# TEXAS INSTRUMENTS

pointer. After this, the pbuf that corresponds to this packet is freed. Thus it is made sure that the freeing of pbuf is done only after the packet transmission is complete.

### 6.3 Packet data reception

Packet reception takes place in the context of the interrupt handler for receive. As described earlier, the receive buffer descriptors are en-queued to the DMA before the reception can actually begin. The pbuf allocated for maximum length, may actually contain a chain of packet buffers. The descriptors are updated for OWNER flag only. The EOP, SOP and EOQ are updated by the DMA upon completion of the reception. One important point to note is that, the actual data received may be less/more than the max length allocated. Hence the pbuf chain needs to be adjusted as detailed here. First, the active\_head (which is the first BD en-queued), is checked for OWNER bit having been cleared by the DMA. Then the BD list is traversed, starting at the active\_head, to find the EOP BD, which is the last BD of the current packet. While doing so if the EOP is not found on the current BD, then the pbuf of the current BD is chained to the pbuf of the next BD, since the current packet has spilled over to the next BD. Once, the EOP is found the last pbuf is updated as the terminator (pbuf->next = NULL). Thus, the entire packet is collected and passed to the upper layer for processing. Since, the current BD has been done with, it is put back at the free\_head, by allocating a new pbuf.

#### 6.4 IwIP Application Layer

This layer contains the Ethernet application (HTTP server, echo server, etc.). This is located at lwip-

1.4,1/apps/<application>. This is the layer at which all the imcoming packets terminate and all outgoing packets originate. This release contains a httpserver\_raw application that runs a sample webserver on the device.

### 6.5 System Application Layer

This layer implements system level initialization and provides options for IwIP stack. This layer can contain any other algorithms, decoding, etc. The main IP stack based application is part of the lwip directory as mentioned above.

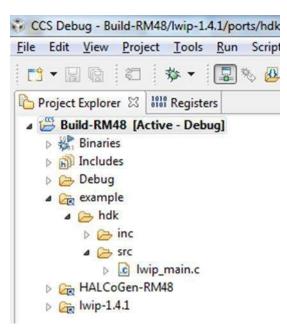

### 7 Release Folder Structure

There are 6 different variants supported. The folder for each variant contains the following:

- **Build Folder**: This contains the Code Composer Studio project which can be imported into your workspace and built.

- **HALCoGen Folder**: This folder contains the source and include folders generated using the latest version on HALCoGen.

- **Demo Executable**: This folder contains a .out file which can be executed on the device HDK that is being used for development.

Note:

- The 'Build-xx' folder contains the CCSv5 project for the device.

- The 'HALCoGen-xx' folder contains the HALCoGen generated driver files for the device.

- The 'Demo Executable' Folder contains the .out file for the sample project for the device, which can be loaded and executed.

- The 'example' folder contains a HDK port of the lwIP example.

- 'lwip-1.4.1' contains all the lwIP library files.

#### 8 Hardware Setup

- Connect ethernet port on HDK to network with DHCP Server

- Enable the Ethernet on EVM by setting switch S2 bit4 to On

Connect the JTAG USB port to PC (used for console output also)

#### 9 Building and Executing

- Release folders contains CCS Projects for RM48xx and RM46xx(Little Endian) & TMS570xx Devices (Big

- Endian).

- Based on the device import the project into CCS from <install\_folder>\<device line>

- Build the project

- Target configuration, is supplied with this software. Set the correct target configuration as the Default & Active configuration

Download and execute the binary (Disconnect the device from debugger and reset). Below is an screen capture of console output:

```

E Console 🖉 Terminal 🔀

Serial: (COM6, 9600, 8, 1, None, None - CONNECTED) - Encoding: (ISO-8859-1)

HERCULES MICROCONTROLLERS

Texas Instruments

Little Endian device

Initializing ethernet (DHCP)

DEBUG - Getting PHY ID....SUCCESS

DEBUG - Getting PHY Alive Status...SUCCESS

DEBUG - Getting PHY Link Status...SUCCESS

DEBUG - Setting up Link...SUCCESS

..DONE

Starting Web Server..DONE

HERCULES MICROCONTROLLERS

Texas Instruments

Little Endian device

Device IP Address: 172.24.190.172

Webserver accessible @ http:\\172.24.190.172

```

The webserver is accessible at the IP address displayed in the console.

#### Note on Demo Build

The project settings have already been set and it can be built and executed straight out of the box. Some files and folders from the LWIP library are excluded from the CCS Build. For reference, this is the list of excluded files. (To exclude a file or a folder from build, right click on it and select 'Resource Configurations' and click 'Exclude from Build') :

- i. lwip-1.4.1/apps/httpserver\_raw/makefsdata

- ii. lwip-1.4.1/apps/httpserver\_raw/fsdata.c

- iii. lwip-1.4.1/ports/hdk/netif/hdkif.c

- iv. lwip-1.4.1/ports/hdk/locator.c

- v. lwip-1.4.1/ports/hdk/perf.c

- vi. lwip-1.4.1/ports/hdk/sys\_arch.c

- vii. lwip-1.4.1/src/api

- viii. lwip-1.4.1/src/core/ipv4

- ix. lwip-1.4.1/src/core/snmp

- x. lwip-1.4.1/src/core/\*.c (Except def.c and timers.c, which are required).

- xi. lwip-1.4.1/src/netif/ppp/\*.c (All C files in this folder).

- xii. lwip-1.4.1/src/netif/etharp.c

- xiii. lwip-1.4.1/src/netif/loopif.c

# TEXAS INSTRUMENTS

- xiv. lwip-1.4.1/src/netif/slipif.c

- xv. lwip-1.4.1/test

The following file paths are added in the include path (Already included)

- i. lwip-1.4.1/ports/hdk/check

- ii. lwip-1.4.1/apps/httpserver\_raw

- iii. lwip-1.4.1/src/include/ipv4

- iv. lwip-1.4.1/ports/hdk/include/netif

- v. lwip-1.4.1/ports/hdk/include

- vi. lwip-1.4.1/ports/hdk/netif

- vii. halcogen-rm48/include

- viii. lwip-1.4.1/ports/hdk

- ix. lwip-1.4.1

- x. example/hdk/inc

- xi. lwip-1.4.1/src/include