## **BIOS MCSDK 2.0**

# **PCIE Boot Example**

Applies to patch release based on 02.00.01.12 Publication Date: August 12, 2011

Version 1.2

Texas Instruments, Incorporated 20450 Century Boulevard Germantown, MD 20874 USA

### **Document License**

This work is licensed under the Creative Commons Attribution-NoDerivs 3.0 Unported License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nd/3.0/ or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

Contributors to this document

Copyright (C) 2011 Texas Instruments Incorporated - http://www.ti.com

© Copyright 2011 Texas Instruments, Inc.

All Rights Reserved

## **Contents**

| Overview                                         | 1                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision History                                 | 1                                                                                                                                                                                                                                                                                                                                       |

| References                                       | 1                                                                                                                                                                                                                                                                                                                                       |

| DDR Init Boot Image                              | 1                                                                                                                                                                                                                                                                                                                                       |

| 4.1 Procedure to build ddrinit                   | 2                                                                                                                                                                                                                                                                                                                                       |

| HelloWorld Boot Image                            | 2                                                                                                                                                                                                                                                                                                                                       |

| 5.1 Procedure to build HelloWorld                | 2                                                                                                                                                                                                                                                                                                                                       |

| POST Boot Image                                  | 3                                                                                                                                                                                                                                                                                                                                       |

| 6.1 Procedure to prepare POST boot image         | 3                                                                                                                                                                                                                                                                                                                                       |

| PCIE Linux Host Loader Code                      | 3                                                                                                                                                                                                                                                                                                                                       |

| 7.1 Procedure to build and run Linux host loader | 4                                                                                                                                                                                                                                                                                                                                       |

| 7.2 How HelloWorld boot example works            | 5                                                                                                                                                                                                                                                                                                                                       |

| 7.3 How POST boot example works                  | 5                                                                                                                                                                                                                                                                                                                                       |

| Test Setup and Expected Results                  | 5                                                                                                                                                                                                                                                                                                                                       |

|                                                  | References DDR Init Boot Image  4.1 Procedure to build ddrinit HelloWorld Boot Image  5.1 Procedure to build HelloWorld POST Boot Image  6.1 Procedure to prepare POST boot image PCIE Linux Host Loader Code  7.1 Procedure to build and run Linux host loader  7.2 How HelloWorld boot example works  7.3 How POST boot example works |

# **PCIE Boot Example**

#### 1 Overview

The PCIE boot example is created to help customer quickly boot DSP through PCIE. The boot example includes:

- A HelloWorld boot example from all cores, which has two CCS projects to build the DDR initialization boot image and HelloWorld boot image.

- A simple POST boot example from core 0 in addition to HelloWorld boot example.

- Linux host PCIE loader code to map between PC memory and DSP memory. It loads the boot example into DSP via PCIE for boot demo purpose.

## 2 Revision History

| Revision | Details                                   |

|----------|-------------------------------------------|

| 1.2      | Add support of 6670                       |

| 1.1      | Add a new PCIE boot demo for "HelloWorld" |

| 1.0      | Initial Version                           |

#### 3 References

[1] KeyStone Architecture Peripheral Component Interconnect Express (PCIe) User Guide (Rev. A, http://www.ti.com/litv/pdf/sprugs6a)

## 4 DDR Init Boot Image

The DDR Init project uses the BIOS MCSDK Platform Library to initialize the DDR.

#### 4.1 Procedure to build ddrinit

- Import the project from tools\boot\_loader\examples\pcie\pcieboot\_ddrinit\evmc66xxl in CCSv5

- Clean and re-build the project

- The pcieboot\_ddrinit\_evm66xxl.map and pcieboot\_ddrinit\_evm66xxl.out will be generated under tools\boot\_loader\examples\pcie\pcieboot\_ddrinit\evmc66xxl\bin. Note the local L2 memory used by .out file can't be used by user applications, please check the .map file for details, the magic address (0x0087FFFC for TMS320C6678; 0x008FFFFC for TMS320C6670) can't be used as well.

- Run pcieboot\_ddrinit\_elf2HBin.bat under tools\boot\_loader\examples\pcie\pcieboot\_ddrinit\evmc66xxl\bin, the batch file does the following file conversion:

- Uses Code Gen utility hex6x.exe utility to convert the ELF format .out file to a ASCII hex format boot table file

- Uses Bttbl2Hfile.exe to convert the boot table file to a header text file.

- Uses hfile2array.exe to convert the header text file to a header file with array of the image data

- Moves the converted header file to tools\boot\_loader\examples\pcie\linux\_host\_loader folder

## 5 HelloWorld Boot Image

The HelloWorld project uses the BIOS MCSDK Platform Library to initialize the UART, it will print the "Hello World" and booting information for all the DSP cores to the UART once it runs.

#### 5.1 Procedure to build HelloWorld

- Import the project from tools\boot\_loader\examples\pcie\pcieboot\_helloworld\evmc66xxl in CCSv5

- Clean and re-build the project

- The pcieboot\_helloworld\_evm66xxl.map and pcieboot\_helloworld\_evm66xxl.out will be generated under tools\boot\_loader\examples\pcie\pcieboot\_helloworld\evmc66xxl\bin. Note the DDR memory (common code to all cores) used can't be used by user applications; also some local L2 used by individual cores (.stack, .bss, ...) can't be used by user applications. Please check the .map file for details.

• Run helloworld\_elf2HBin.bat under tools\boot\_loader\examples\pcie\pcieboot\_helloworld\evmc66xxl\bin, the batch file does the same file conversion as pcieboot\_ddrinit\_elf2HBin.bat does.

### 6 POST Boot Image

The existing POST is used as another PCIE boot example. The POST uses the BIOS MCSDK Platform Library to do a board test and results can be displayed via UART.

#### 6.1 Procedure to prepare POST boot image

Run pcieboot\_post\_elf2HBin.bat under tools\boot\_loader\examples\pcie\pcieboot\_post\evmc66xxl\bin, the batch file first copy post\_evm66xxl.out from tools\post\evmc66xxl\bin to tools\boot\_loader\examples\pcie\pcieboot\_post\evmc66xxl\bin folder, then it does the same file conversion as pcieboot\_ddrinit\_elf2HBin.bat does as well.

#### 7 PCIE Linux Host Loader Code

The PCIE Linux host loader code has several functions:

- Do a memory mapping between PC memory and DSP memory (4 blocks of memories are requested by DSP via PCIE registers BAR0, BAR1, BAR2 and BAR3 masks:

- o For 6678: 4K, 512K, 4M and 16M respectively for PCIE application registers, local L2, shared L2 and DDR3;

- For 6670: 4K, 1M, 2M and 16M respectively for PCIE application registers, local L2, shared L2 and DDR3.

The BAR masks are configured inside PCIE initialization code when selects PCIE boot mode on EVM.

• Configure the PCIE inbound address translation through the accessing of application registers as below example for IB\_BARn, IB\_STARTn\_LO, IB\_STARTn\_HI and IB\_OFFSETn (n = 0, 1, 2, 3).

- Provide DSP memory read/write API:

- Uint32 ReadDSPMemory(Uint32 coreNum, Uint32 DSPMemAddr, Uint32 \*buffer, Uint32 length)

- Uint32 WriteDSPMemory(Uint32 coreNum, Uint32 DSPMemAddr, Uint32 \*buffer, Uint32 length)

- Parse the boot example header array file for boot entry address, section size and start address of sections and load the boot data into DSP memory via API.

- Write the boot entry address into the magic address on core 0 via API.

#### 7.1 Procedure to build and run Linux host loader

- Create a folder (e.g. pcie\_test) in a Linux machine. Copy pciedemo.c, Makefile, pcieDdrInit\_66xx.h, pcieBootCode\_66xx.h and post\_66xx.h from tools\boot\_loader\examples\pcie\linux\_host\_loader to the folder.

- Change directory to "pice\_test", update KDIR inside Makefile to your system (you can find it out by "uname –a" command)

- Type "make", a pciedemo.ko file should be created

- By default, this will build the "HelloWorld" demo on 6678, which is controlled by the following Marcos in peiedemo.c:

```

#define HELLO_WORLD_DEMO 1

#define POST_DEMO 0

#define EVMC6678L 1

#define EVMC6670L 0

```

If you want to build the POST demo or 6670 demos, please toggle those between 0 and 1 accordingly. E.g., for POST demo on 6670:

```

#define HELLO_WORLD_DEMO 0

#define POST_DEMO 1

#define EVMC6678L 0

#define EVMC6670L 1

```

Then, type "make clean" and type "make" to rebuild the pciedemo.ko.

• To insert the module into kernel, type "sudo insmod pciedemo.ko"; to view the kernel message, type "dmesg"; to remove the module from kernel, type "sudo rmmod pciedemo.ko"

#### 7.2 How HelloWorld boot example works

The Linux host first pushes the DDR init boot image data to L2 memory of core 0, then writes the boot entry address of the DDR init boot image to the magic address on core 0, both via PCIE. When the EVM is in PCIE boot mode, the IBL code running on the DSP core 0 polls the entry address and jumps to that address and starts to boot (initialize the DDR). After DDR is properly initialized, the DDR init code clears the magic address and keeps on polling it.

Linux host then pushes the HelloWorld boot image data to DDR memory, then writes the boot entry address of the HelloWorld boot image to the magic address on core 0 to boot core 0. Core 0 starts to boot and print the "Hello World" booting information, and then boot all the other cores by writing the address of \_c\_int00 to the magic address on other cores and sending an IPC interrupt to other cores. The RBL running on other cores will jump to \_c\_int00 and start to boot, each core will write 0xBABEFACE to its magic address by running a function write\_boot\_magic\_number().

Note that Host boot application needs to wait for some time after pushing the DDR init boot image and before pushing the HelloWorld boot image to the DDR, this will ensure DDR is properly initialized.

#### 7.3 How POST boot example works

The POST example uses L2 only. The Linux host first pushes the POST boot image data to L2 memory of core 0, then writes the boot entry address of the POST to the magic address on core 0, both via PCIE. The IBL code running on the DSP core 0 polls the entry address and jumps to that address and starts to boot.

**Note:** It is IBL (in local L2) that monitors magic address and boots the DDR init (in local L2) or POST (in local L2) in those two demos. If one wants to load his/her own boot demo code, then it shouldn't overlap with the IBL code. As a guideline, the IBL uses memory from 0x008000000 to 0x0081BDFF. To check the exact memory usage, you can re-build the IBL by following the instructions in tools\boot\_loader\ibl\doc\build\_instructions.txt and check the resulting ibl\_c66x\_init.map file. In addition, following local L2 is reserved by RBL and shouldn't be used: for 6678 ROM PG 1.0, 0x00872DC0 – 0x0087FFFF; for 6670 ROM PG 1.0, 0x008F2DC0 – 0x008FFFFF.

## 8 Test Setup and Expected Results

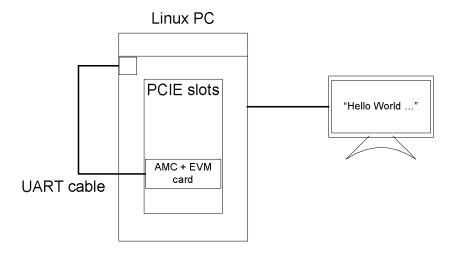

An AMC to PCIE adaptor card, a TMS320C66xxL EVM card and a Linux PC are required to do the test, as the diagram shown below:

The test is verified on both TMS320C6670L and TMS320C6678L cards, with a 32-bit Linux PC running Ubuntu 10.04. Other 32-bit Linux OS are expected to work as well.

- Before connect the system, please update IBL with the latest from MCSDK by following the steps 1) and 2) in tools\boot\_loader\ibl\doc\evmc66xx-instructions.txt. For step 1), Programing "IBL" on the EEPROM at bus address 0x51, make sure using "swap\_data = 0" in tools\writer\eeprom\evmc66xxl\bin\eepromwriter input.txt.

- Set EVM card to PCIE boot via following switch setting:

| SW3                | SW4              | SW5               | SW6               | SW9    |

|--------------------|------------------|-------------------|-------------------|--------|

| (pin1, 2, 3, 4)    | (pin1, 2, 3, 4)  | (pin1, 2, 3, 4)   | (pin1, 2, 3, 4)   | (pin1) |

| (off, on, on, off) | (on, on, on, on) | (on, on, on, off) | (off, on, on, on) | (on)   |

- Assemble the EVM card into the adaptor card

- UART port can be accessed either through Mini-USB connector (USB1) or through 3-pin RS232 Serial port header (COM1). The selection can be made through UART route select connector COM\_SEL1 as follows:

- UART over USB Connector (Default): Shunts installed over COM\_SEL1.3-COM\_SEL1.1 and COM\_SEL1.4-COM\_SEL1.2

- UART over 3-Pin Header LAN1: Shunts installed over COM\_SEL1.3-COM\_SEL1.5 and COM\_SEL1.4-COM\_SEL1.6

- Connect the URAT cable from EVM card to a Linux PC's USB port or serial port based on the desired access method

- Completely shut off the PC power supply (by disconnecting the power cord), insert the AMC adaptor card (with TMS320C66xxL EVM card mounted) into an open PCIE slot in PC's motherboard

- Supply the power to PC, wait for a few seconds and power on the PC.

- Make sure the PCIE device is correctly enumerated by PC by checking below, note DEVICE\_ID field is changed from 0x8888 to 0xb005 which is programmed in IBL.

- Either enter PC's BIOS setting when PC is booting up, a new PCIE device should be populated in the PCIE slot where Shannon card is inserted, shown as a "Multimedia device".

- Or, type "lspci –n" under Linux command shell after Linux OS is loaded, a TI device (VENDOR\_ID: 0x104c) should be in the list:

```

local-ubuntu:~$ lspci -n

00:00.0 0600: 8086:2774

00:1b.0 0403: 8086:27d8 (rev 01)

....

00:1f.3 0c05: 8086:27da (rev 01)

01:00.0 0480: 104c:b005 (rev 01)

03:00.0 0200: 14e4:1677 (rev 01)

Similarly, one can type "lspci",

local-ubuntu:~$ lspci

....

00:1f.3 SMBus: Intel Corporation N10/ICH 7 Family SMBus Controller (rev 01)

01:00.0 Multimedia controller: Texas Instruments Device b005 (rev 01)

....

```

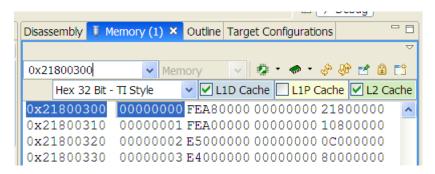

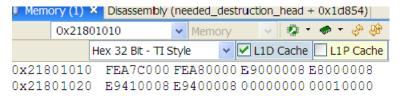

The PCIE BARn (n = 0, 1, 2, ..., 5) registers are written by Linux PC after enumeration, they should be non-zero. Optionally, if a JTAG emulator is available, one can verify this by looking at address starting from 0x21801010 for 6 32-bit word. Below is an example.

- Prepare pciedemo.ko in the Linux PC, please refer to section 7.1

- On the Linux PC open a new terminal window to run minicom. First run "sudo minicom –s" to set the correct configuration: 115200bps, 8-N-1, Hardware flow control: OFF, Software flow control: OFF, and select the correct Serial Device. Save then run "sudo minicom" to monitor the port.

- Type "sudo insmod pciedemo.ko",

- o For the HelloWorld demo, one should see the following printed on the minicom

#### 6678 example:

```

Compiled on Jan 25 2010, 06:49:09.

Port /dev/tty50

Press CTRL-A Z for help on special keys

PCIE Boot Hello World Example Version 01.00.00.00

Booting Hello World image on Core 0 from PCIE ...

Booting Hello World image on Core 1 from Core 0 ...

Booting Hello World image on Core 2 from Core 0 ...

Booting Hello World image on Core 3 from Core 0 ...

Booting Hello World image on Core 4 from Core 0 ...

Booting Hello World image on Core 5 from Core 0 ...

Booting Hello World image on Core 6 from Core 0 ...

Booting Hello World image on Core 7 from Core 0 ...

```

#### 6670 example:

```

Welcome to minicom 2.4

OPTIONS: I18n

Compiled on Jan 25 2010, 06:49:09.

Port /dev/ttyS0

Press CTRL-A Z for help on special keys

PCIE Boot Hello World Example Version 01.00.00.00

Booting Hello World image on Core 0 from PCIE ...

Booting Hello World image on Core 1 from Core 0 ...

Booting Hello World image on Core 2 from Core 0 ...

Booting Hello World image on Core 3 from Core 0 ...

```

Optionally, if a JTAG emulator is available, one can verify that the PC registers for cores other than core 0 should be inside DDR; and magic address for cores other than core 0 should be written with 0xBABEFACE.

o For the POST demo, one should see the following printed on the minicom

#### 6678 example:

```

TMDXEVM6678L POST Version 01.00.00.03

FPGA Version: 000B

Board Serial Number: ECD0032489

EFUSE MAC ID is: 90 D7 EB 0D 12 56

SA is disabled on this board.

PLL Reset Type Status Register: 0x00000001

POST running in progress ...

POST I2C EEPROM read test started!

POST I2C EEPROM read test passed!

POST SPI NOR read test started!

POST SPI NOR read test passed!

POST EMIF16 NAND read test started!

POST EMIF16 NAND read test passed!

POST EMAC loopback test started!

POST EMAC loopback test passed!

POST external memory test started!

POST external memory test passed!

POST done successfully!

```

#### 6670 example:

```

🔞 📀 🚫 a0271557@a0271557local-ubuntu: ~

File Edit View Terminal Help

TMDXEVM6670L POST Version 01.00.00.03

FPGA Version: 0006

Board Serial Number: ESE0083053

EFUSE MAC ID is: 90 D7 EB A4 BC AC

SA is disabled on this board.

PLL Reset Type Status Register: 0x00000001

POST running in progress ...

POST I2C EEPROM read test started!

POST I2C EEPROM read test passed!

POST SPI NOR read test started!

POST SPI NOR read test passed!

POST GPIO NAND read test started!

POST GPIO NAND read test passed!

POST EMAC loopback test started!

POST EMAC loopback test passed!

POST external memory test started!

POST external memory test passed!

POST done successfully!

```

To view the kernel log, one can type "dmesg"

[ 315.710097] Boot entry address is 0x8000c9e0

o Hello World:

```

6678 example:

```

```

[ 315.662991] Finding the device....

[ 315.663005] Found TI device

[ 315.663009] TI device: vendor=0x0000104c, dev=0x0000b005, drv=0x00000000, irq=0x00ff, bus=0xf74ca400

[ 315.663011] Reading the BAR areas....

[ 315.663866] Enabling the device....

[ 315.663884] pci 0000:01:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16

[ 315.663891] pci 0000:01:00.0: setting latency timer to 64

[ 315.663906] Access PCIE application register ....

[ 315.663910] Boot entry address is 0x1082c880

[ 315.665831] Total 4 sections, 0xd3c0 bytes of data written to core 0

```

[ 315.711802] Total 4 sections, 0xd67c bytes of data written to core 9

```

6670 example:

```

- [ 253.447546] Finding the device....

- [ 253.447559] Found TI device

- [ 253.447562] TI device: vendor=0x0000104c, dev=0x0000b005, drv=0x00000000, irq=0x000b, bus=0xf74ca400

- [ 253.447565] Reading the BAR areas....

- [ 253.448561] Enabling the device....

- [ 253.448580] pci 0000:01:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16

- [ 253.448586] pci 0000:01:00.0: setting latency timer to 64

- [ 253.448601] Access PCIE application register ....

- [ 253.448605] Boot entry address is 0x1082d1a0

- [ 253.450600] Total 4 sections, 0xddc0 bytes of data written to core 0

- [ 253.532113] Boot entry address is 0x8000d300

- [ 253.533898] Total 4 sections, 0xe07c bytes of data written to core 9

#### o POST:

#### 6678 example:

- [ 192.367639] Finding the device....

- [ 192.367658] Found TI device

- [ 192.367663] TI device: vendor=0x0000104c, dev=0x0000b005, drv=0x00000000, irq=0x00ff, bus=0xf74ca400

- [ 192.367669] Reading the BAR areas....

- [ 192.368931] Enabling the device....

- [ 192.368952] pci 0000:01:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16

- [ 192.368962] pci 0000:01:00.0: setting latency timer to 64

- [ 192.368978] Access PCIE application register ....

- [ 192.368985] Boot entry address is 0x 839ee0

- [ 192.370500] Total 3 sections, 0xa888 bytes of data written to core 0

#### 6670 example:

- [ 176.118474] Finding the device....

- [ 176.118488] Found TI device

- [ 176.118491] TI device: vendor=0x0000104c, dev=0x0000b005, drv=0x000000000, irq=0x00ff, bus=0xf74ca400

- [ 176.118494] Reading the BAR areas....

- [ 176.119282] Enabling the device....

- [ 176.119299] pci 0000:01:00.0: PCI INT A -> GSI 16 (level, low) -> IRQ 16

- [ 176.119306] pci 0000:01:00.0: setting latency timer to 64

- [ 176.119321] Access PCIE application register ....

- [ 176.119325] Boot entry address is 0x 83af80

- [ 176.121022] Total 3 sections, 0xba64 bytes of data written to core 0